En el desarrollo de esta practica se plantea realizar una ALU la cual realice 4 operaciones (2 logicas y 2 aritmeticas) la cual sera controloda por una maquina de estados (PC) dandonos la seleccion de la operacion. como implementaremos 4 operaciones necesitamos 2 bits de salida de la maquina de estados:

000 -> suma

001 -> resta

010 -> not

110 -> or

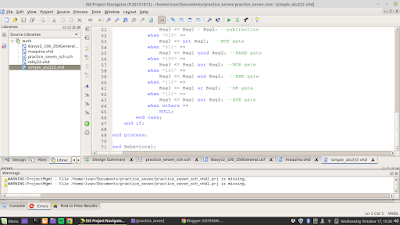

El codigo de la ALU es el siguiente:

Como se puede observar el codigo es muy sencillo y cuenta con mas operaciones de las que se implementaran en este practica, se añade este codigo de la misma manera como se ha venido trabajando, se hace necesario implementar una maquina de estados la cual dara a la salida las posiciones de la operacion deseada este a su vez necesita de un reloj que dara la velocidad de cambio entre las operaciones, la maquina de estados sera la siguiente:

Al implementar este codigo observamos que la FPGA realiza las cuatro operaciones mostrando una por una en los leds de la tarjeta, dependiendo de las entradas que ingresemos nosotros en los switchs, obteniendo de esta manera un pequeño procesador con su programa de control y su ALU.

No hay comentarios.:

Publicar un comentario